Programowanie FLASH

Niniejszy artykuł, przedstawiając podstawy technologii pamięci Flash, ma za zadanie wyrobić intuicję do zrozumienia istoty problemów na jakie się napotyka przy użytkowaniu scalonych układów pamięci Flash.

Zapraszamy do zapoznania się z ofertą WG Electronics w obszarze programatorów, obejmującej programatory Flash renomowanych firm:

Technologia pamięci FLASH

Nie wnikając w szczegóły technologii, historycznie programując pamięci nieulotne zapisywaliśmy bezpośrednio mapę bitową tzn. pod konkretny adres wpisywaliśmy odpowiedni bajt impulsem o zdefiniowanym czasie trwania i podwyższonym napięciu. Tak było z układami EEPROM (Electrically Erasable Programable Read-Only Memory). Zapis zmieniał poprzednią zawartość. Operacja programowania nie wymagała więc wcześniejszego kasowania zawartości, jak chociażby we wcześniejszych układach EPROM kasowanych w całości światłem UV. Współcześnie stosowane pamięci nieulotne - układy Flash, są wykonane jeszcze w innej technologii. Mają też zupełnie inną architekturę, wielkie pojemności i inny sposób programowania. Zapis wymaga wcześniejszego skasowania zawartości gdyż inne zjawiska fizyczne leżą u podstaw operacji kasowania i zapisu. Stwarzają więc zupełnie inne problemy przy ich zapisie niż EEPROM.

Spróbujmy poglądowo przedstawić istotę technologii pamięci FLASH.

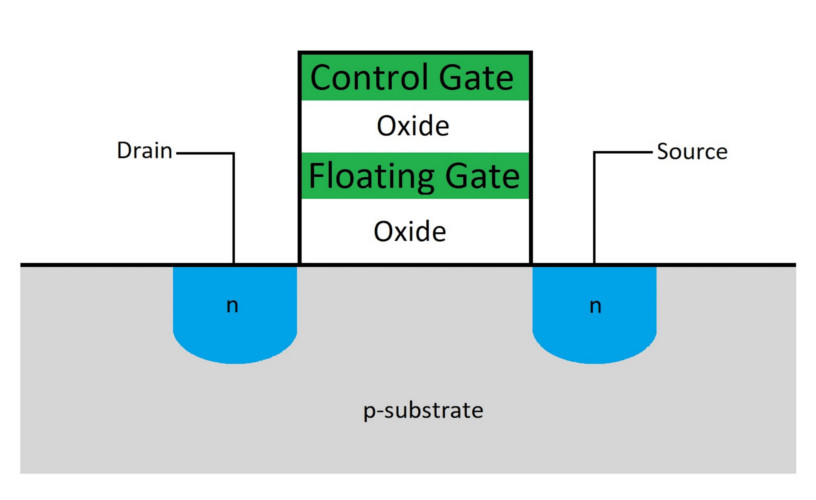

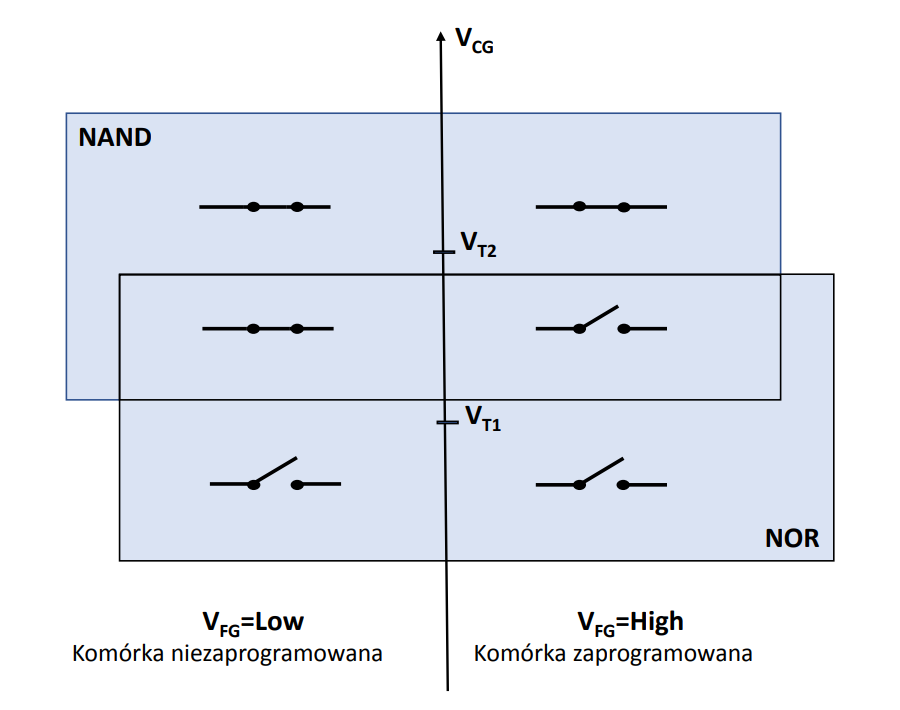

Podstawowa komórka pamięci jest zbudowana na bazie tranzystora MOSFET z dodatkową tzw. pływającą bramką FG (Floating Gate). Ta bramka „dubluje” bramkę sterującą CG (Control Gate). Pojedyncza komórka pamięci może być w uproszczeniu traktowana jako elektroniczny przełącznik, sterowany bramkami sterującą i pływającą, włączający/wyłączający przepływ prądu między źródłem i drenem. Skasowana komórka, bez ładunku w pływającej bramce, włączy się po podaniu sygnału o napięciu wyższym od pewnej wartości progowej VT1 na bramkę kontrolną i będzie przedstawiać pierwszą wartość logiczną – powiedzmy 0. Zaprogramowana komórka, z ładunkiem w pływającej bramce, ekranuje pole elektryczne bramki sterującej i podwyższa napięcie progowe załączenia do VT2 - blokuje bramkę sterującą. Komórka zaprogramowana po podaniu napięcia z zakresu (VT1,VT2) nie włączy się i będzie przedstawiać drugą wartość logiczną – powiedzmy 1. Po podaniu napięcia powyżej VT2 zarówno skasowana jak i zaprogramowana komórka włączą się.

Spójrzmy jeszcze na powyższy diagram przedstawiający stany klucza MOSFET w zależności od napięcia na bramce sterującej VCG i obecności ładunku w bramce pływającej VFG. Jak widać komórka pamięci FLASH zapewnia implementację zapamiętywania bitu cyfrowej informacji, zarówno w logice prostej jak i odwrotnej, jest logicznie funkcjonalnie pełna. Szeregowe lub równoległe połączenie tych komórek pamięci pozwala więc na realizację matryc czyli realizację układów pamięci.

Bramka pływająca jest izolowana, zachowuje ładunek po wyłączeniu zasilania. Operacja programowania polega więc na wprowadzeniu odpowiedniego ładunku do bramki pływającej w tzw. procesie tunelowania, a kasowania na usunięciu ładunku w procesie odwrotnym.

Pamięć FLASH zorganizowana jako matryca przedstawionych powyżej komórek pamięci w pojedynczej komórce typu SLC (Single-Level Cell) może pamiętać jeden bit informacji. W bardziej rozbudowanych układach, w komórkach typu MLC (Multi-Level Cell) w tym TLC (Triple-Level Cell) może pamiętać więcej bitów. Jest to osiągane przez różne poziomy ładunku w pływającej bramce FG.

Dwa główne typy pamięci Flash wzięły swoje nazwy od nazw bramek logicznych NOR i NAND co odzwierciedla sposób połączenia poszczególnych komórek pamięci w matrycy pamięci Flash. I tak…

NOR FLASH

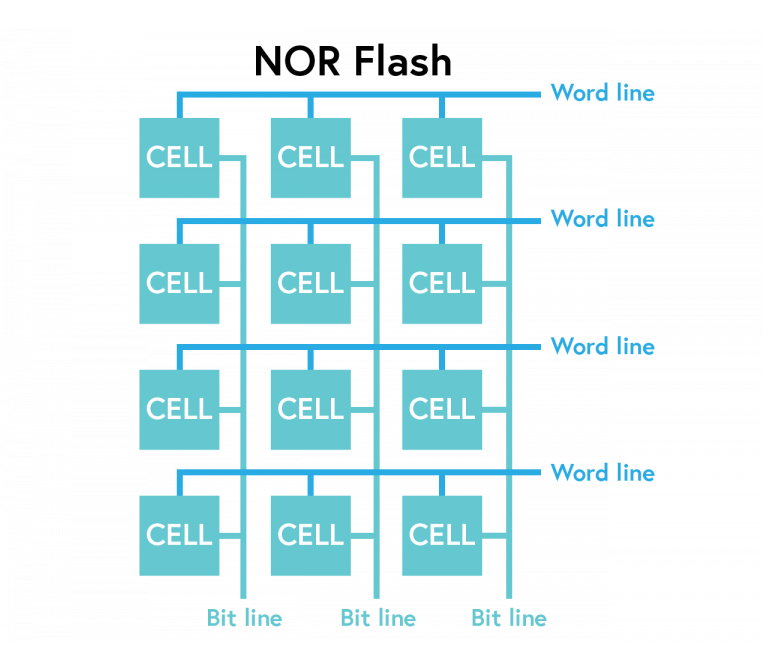

Odpowiada równoległemu połączeniu komórek pamięci. Wtedy stan na linii odpowiadającej danemu bitowi będzie miał wartość logiczną 0, gdy co najmniej jedna z komórek pamięci dołączonych równolegle do tej linii się włączy po podaniu sygnału wyboru tej komórki pamięci po zdekodowaniu adresu słowa. Bramka pamięci NOR w stanie spoczynkowym, nie wysterowanym musi więc być zamknięta.

Pamięć NOR jest matrycą takich komórek. Jej architektura jest analogiczna do równoległych pamięci EEPROM – wybór słowa po liniowym zdekodowaniu adresu powoduje odczyt całego zapamiętanego słowa. Tak więc NOR jest preferowany w aplikacjach zintegrowanych (m.in. w mikrokontrolerach) zarówno do zapamiętywania kodu jak i danych.

W takiej strukturze aby odczytać dane, należy większość linii słów wysterować poniżej wartości VT1 niezaprogramowanej komórki. Wszystkie klucze MOSFET (zaprogramowane i niezaprogramowane) podpięte do tych linii pozostaną otwarte nie wpływając na stan linii bitów. Tylko jedną linię słowa odpowiadającą zdekodowanemu adresowi należy wysterować poniżej wartości VT2 zaprogramowanej komórki, a powyżej VT1 niezaprogramowanej komórki. Klucze MOSFET niezaprogramowanych komórek wybranego słowa ściągną wtedy linie bitów w dół. W zaprogramowanych komórkach słowa, klucze pozostaną otwarte, a linie bitów w stanie wysokim.

Ze względu na liniowe adresowanie słów pamięci NOR, analogiczne do równoległych pamięci EEPROM oraz zastosowanie jako pamięci firmware’u BIOS oczekuje się, że NOR FLASH będzie wolne od strukturalnych wad

NAND FLASH

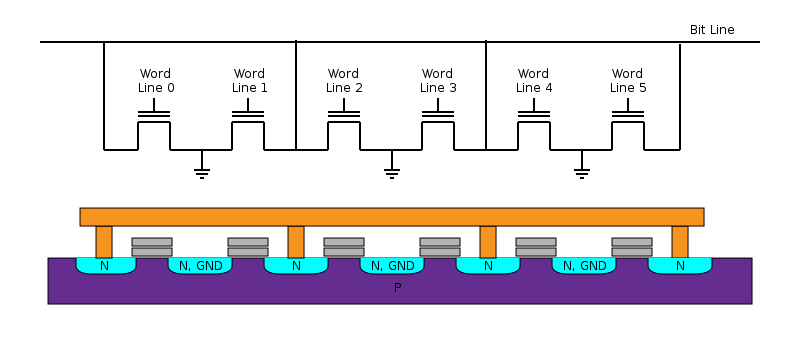

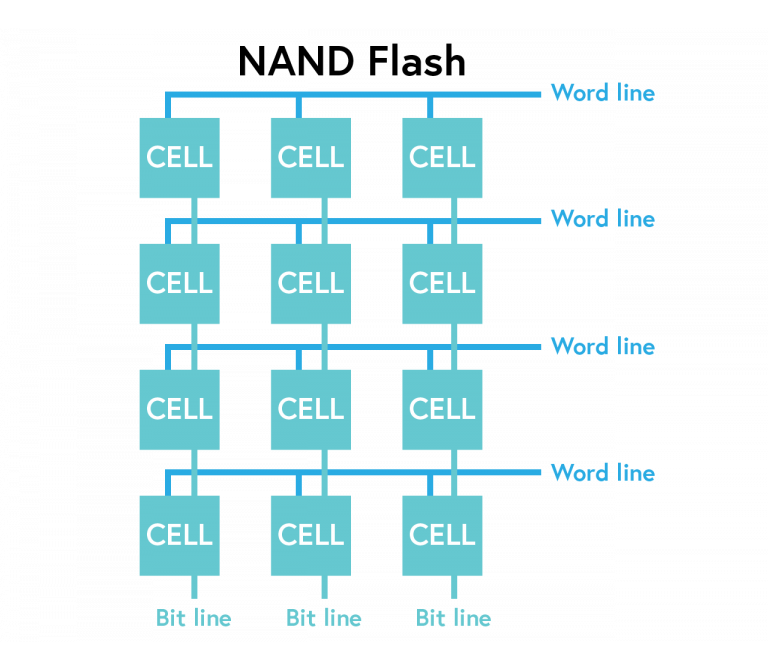

Odpowiada szeregowemu połączeniu komórek pamięci. Wtedy stan na linii odpowiadającej danemu bitowi odpowiada wartości 0, gdy wszystkie komórki szeregowo dołączone do tej linii są włączone, łącznie z wybraną zdekodowanym adresem.

Należy zwrócić uwagę, że logika układów NAND jest odwrotna w stosunku do NOR. W stanie spoczynkowym, niewysterowanym bramka musi być zamknięta.

Z logicznego punkty widzenia komórki NAND można połączyć w matrycę jak poniżej i mieć układ pamięci cyfrowej analogiczny do NOR tylko w logice odwrotnej.

Jednak współcześnie układy pamięci NAND są realizowane inaczej. Łańcuch NAND szeregowo połączonych komórek pamięci jest podłączany w strukturę NOR w miejsce pojedynczych tranzystorów MOSFET. Jest to możliwe dzięki dodatkowym kluczom w łańcuchu MOSFET, które dołączają/odłączają łańcuchy do/od linii bitów/uziemienia. W porównaniu do układów pamięci NOR architektura ta wprowadza więc dodatkowy poziom adresowania. Oprócz adresowania stron i słów dochodzi adresowanie bitów.

W takiej strukturze aby odczytać dane, najpierw wybiera się żądaną grupę (łańcuch) w sposób analogiczny do wyboru pojedynczej komórki z kluczem MOSFET w matrycy NOR. Następnie w łańcuchu większość linii słowa należy wysterować powyżej wartości VT2 zaprogramowanej komórki. Tylko jedną, wybraną linię należy wysterować powyżej wartości VT1 niezaprogramowanej komórki, a poniżej VT2 zaprogramowanej komórki. Łańcuch ściągnie wtedy linię bitu w dół, tylko wtedy gdy wybrany bit nie został zaprogramowany.

Wszystko to uzasadnia blokową i stronicową architekturę pamięci NAND. Daje intuicję dlaczego pewne operacje jak kasowanie, zapis realizowane są na pełnych blokach pamięci, a nie na pojedynczych komórkach. Taka trudniejsza do zarządzania struktura matrycy pamięci jest kosztem, za dużo większe upakowanie kluczy MOSFET w strukturach NAND czyli za osiąganie dużo większych pojemności pamięci typu NAND.

Intuicyjnie widać też, że zarządzanie adresowaniem wymaga kontrolera dostępu. We współczesnych układach NAND FLASH mniej lub bardziej zaawansowany kontroler jest wiec integralną częścią układu pamięci. Spełnia on zwykle znacznie szerszą rolę – koryguje błędy odczytu i maskuje wady fizyczne układów pamięci.

Technologia stosowana w pamięciach FLASH nie jest bowiem w 100% wolna od błędów. Stosowana jest więc suma kontrolna ECC (Error Correction Code lub Error Checking and Correction). Zastosowanie kodów korekcyjnych pozwala na detekcję wadliwego odczytu nawet występującego na wielu bitach i korekcję błędu.

I tak, napięcia potrzebne do zapisu i odczytu komórek mogą powodować niewielkie zmiany ładunku z sąsiednich komórkach, doprowadzając do wystąpienia błędów przy odczycie. Jest to efekt chwilowy, który zostaje naprawiony przy kolejnym zapisie danych do komórki. Kontroler pamięci może odświeżyć zawartość komórki, aby zapobiec utracie danych. Może to robić regularnie lub w przypadku wykrycia zbyt wielu błędów.

Inną wadą pamięci Flash jest ograniczona do około 100.000 (w przypadku komórek MLC nawet mniej) liczba cykli zapisu i kasowania. Stosowanie wysokich napięć prowadzi bowiem do stopniowego uszkadzania komórek, które z czasem są coraz trudniejsze do zaprogramowania i skasowania. Uszkodzenie warstw izolujących wokół pływającej bramki skraca również czas, przez jaki dane mogą zostać utrzymane. Pewne bloki mogą więc ulec awarii w skutek zużycia. I tak, w każdym układzie pamięci, może pojawić się pewna liczba bloków, które nie będą działały poprawnie z powodu defektów czy rozrzutu procesu produkcji. Kontroler wykrywa je na podstawie kodów korekcyjnych, gdy kolejne zapisy nie wykażą poprawy. Kontroler zapamiętuje te bloki i zmienia sposób zapisu danych w matrycy, pomijając wadliwe bloki.

Czas życia pamięci Flash można maksymalizować zapewniając, że liczba cykli zapisu i zerowania dla wszystkich bloków będzie taka sama – dzięki temu zużycie pamięci jest rozłożone równomiernie. Aby to zrealizować, kontroler pamięci musi przechowywać informacje o zużyciu bloków i wybierać najlepszy blok na zapisanie nowych danych.

Współczesne pamięci FLASH

Jak widać z powyższych rozważań, współczesne pamięci Flash wielkiej pojemności nie są pozbawione wad strukturalnych wynikających z samej technologii, procesu produkcji lub zużycia w czasie. Integralną częścią układów Flash są więc skomplikowane kontrolery pamięci zarządzające blokami pamięci, realizujące dostęp w trybie nieliniowego adresowania stronicowego i korygujące odczyt. Stopień komplikacji rośnie wraz z nowymi rozwiązaniami jak 3D, eMMC (embedded Multi Media Card), UFS (Universal Flash Storage) – a końca postępu nie widać.

Liczymy, że powyższe dalekie od naukowych rozważania pomogą w praktyce inżynierskiej gdy przyjdzie do programowania i stosowania nowoczesnych pamięci FLASH.

Zapraszamy także do zapoznania się ze stroną Programatory FLASH.

WG Electronics zapewnia w temacie programowania doradztwo i wsparcie techniczne oparte na ponad 30 letnim własnym doświadczeniu w projektowaniu, produkcji i dystrybucji programatorów oraz na doświadczeniu naszych renomowanych partnerów – wiodących światowych producentów takich urządzeń. Zapraszamy do odwiedzenia stron poświęconych naszym partnerom.